Indexed In

- Open J Gate

- Genamics JournalSeek

- Academic Keys

- JournalTOCs

- ResearchBible

- China National Knowledge Infrastructure (CNKI)

- Scimago

- Ulrich's Periodicals Directory

- Electronic Journals Library

- RefSeek

- Hamdard University

- EBSCO A-Z

- OCLC- WorldCat

- SWB online catalog

- Virtual Library of Biology (vifabio)

- Publons

- MIAR

- Scientific Indexing Services (SIS)

- Euro Pub

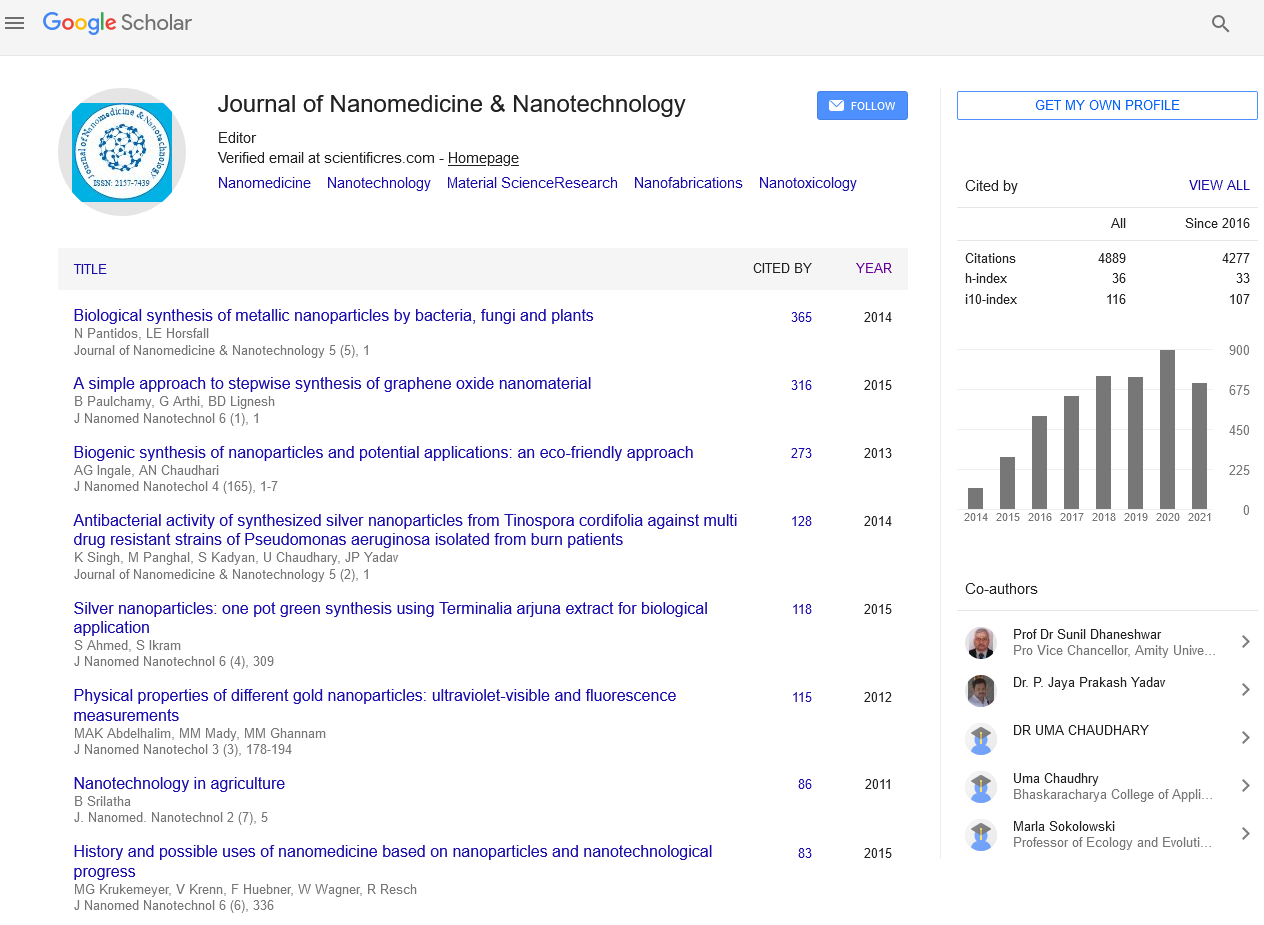

- Google Scholar

Useful Links

Share This Page

Journal Flyer

Open Access Journals

- Agri and Aquaculture

- Biochemistry

- Bioinformatics & Systems Biology

- Business & Management

- Chemistry

- Clinical Sciences

- Engineering

- Food & Nutrition

- General Science

- Genetics & Molecular Biology

- Immunology & Microbiology

- Medical Sciences

- Neuroscience & Psychology

- Nursing & Health Care

- Pharmaceutical Sciences

An 8-channel neural spike feature extraction chip for large-scale neural signal recording in 0.18 üm CMOS

17th International Conference and Exhibition on Nanomedicine and Nanotechnology in Healthcare

November 23-24, 2017 Melbourne, Australia

Peng Li, Xu Zhang, Weihua Pei and Hongda Chen

Institute of Semiconductors-Chinese Academy of Sciences, China

Posters & Accepted Abstracts: J Nanomed Nanotechnol

Abstract:

This paper proposes a low power and efficient neural spike feature extraction chip for large-scale neural signal recording. The communication module, control module and algorithm module are integrated in this chip. To lower power consumption, the algorithm module is designed based on an efficient online feature extraction algorithm (the Dual Vertex Threshold (DVT) and the Minimum Delimitation (MD)), and multiplexing structure is widely used in this chip design, which is beneficial to reduce the area of proposed chip. Fabricated with the 0.18 μm N-well CMOS 1P6M technology, power consumption of this chip is only 5.6357 μW/channel in 1V voltage supply and the neural signal transmission bandwidth is reduced by 98.38%.

Biography :

Peng Li has received BS degree in Electronic Science and Technology from Tianjin University in 2011 and PhD degree in Microelectronics and Solid-State Electronics at Institute of Semiconductors, Chinese Academy of Sciences in 2016. Currently, he is working at Institute of Semiconductors, Chinese Academy of Sciences as an Assistant Professor. His research is focused on signal processing and digital integrated circuit design for biomedical applications.

Email:lipeng@semi.ac.cn